Forschungsprojekt FEntwumS

FPGA-Entwicklungsumgebung zur Systembildung und Visualisierung

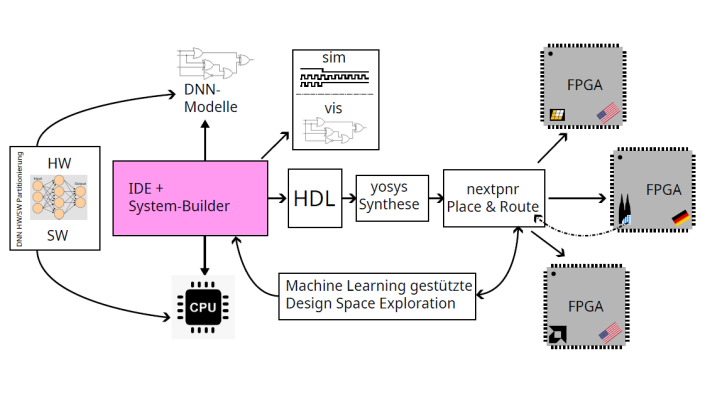

Um FPGAs (Field-Programmable Gate Arrays) nutzen zu können, sind spezielle Software-Werkzeuge erforderlich, die meist in einer Entwicklungsumgebung gebündelt sind. Diese bildet die Schnittstelle, um Hardware effizient zu programmieren. Dabei sind Qualität, Flexibilität und Bedienbarkeit entscheidend. Open-Source-Tools genießen großes Vertrauen, da sie Transparenz bieten. Die Cologne Chip AG ermöglicht durch Offenlegung der internen Strukturen ihrer GateMate-FPGAs die Entwicklung einer Open-Source-basierten Toolchain. Dies steigert die Attraktivität des in Deutschland gefertigten FPGAs und fördert die Technologiesouveränität. Während Open-Source-Tools in Kernaufgaben wie Synthese und Place&Route (P&R) mit kommerziellen Lösungen konkurrieren, fehlen oft intuitive grafische Tools oder Systembuilder. Kommerzielle Tools bieten hingegen umfassende Features wie Debugging, Designvisualisierung und Machine-Learning-Integration. Ziel des Projekts ist es, die Lücke zu schließen, neue Tools für Visualisierung, Analyse und KI-Integration zu entwickeln und diese in bestehende Open-Source-Werkzeuge zu integrieren. Bestehende Tools wie Yosys sollen erweitert werden, um eine durchgängige offene Toolchain für den GateMate-FPGA zu schaffen. Unter Einsatz von Machine Learning gestützter Design Space Exploration werden die Synthese-Ergebnisse hinsichtlich gegebener Kriterien optimiert. Ein weiterer Schwerpunkt ist die Entwicklung von SOPC-Werkzeugen zur Hardware-Software-Kopplung, inklusive passgenauer Unterstützung durch Betriebssysteme, Treiber und Bibliotheken. Neuronale Netzwerke sollen unterstützt werden, indem Hardware- und Softwarelösungen für FPGAs automatisiert bereitgestellt werden. Ziel ist eine transparente, nutzerfreundliche und leistungsfähige Entwicklungsumgebung.

Auf einen Blick

| Kategorie | Beschreibung |

|---|---|

| Forschungsprojekt | FEntwumS: FPGA-Entwicklungsumgebung zur Systembildung und Visualisierung |

| Fakultät | Fakultät für Informations-, Medien- und Elektrotechnik |

| Institut | Institute of Computer and Communication Technology |

| Beteiligte | Prof. Dr. Tobias Krawutschke |

| Sebastian Wittlich | |

| Projektpartner | Fachhochschule Dortmund (Fachbereich Elektrotechnik) |

| Fraunhofer-Institut für Mikroelektronische Schaltungen und Systeme IMS, Dortmund | |

| Cologne Chip AG, Köln | |

| Fördermittelgeber | Bundesministerium für Bildung und Forschung (BMBF) |

| Laufzeit | 05/2024 bis 04/2027 |